Ref: https://note.tonycrane.cc/cs/system/cs1/topic5/

RISC-V ISA

What is ISA?

ISA: Instruction Set Architechture

- Defined group of commands and operations

- To communicate software and hardware

- Different from micro-architechture

What is RISC-V?

An open-source ISA standard

Official website: https://riscv.org/

RISC: Reduced Instruction Set Computing

More ISAs: X86, ARM, Power, MIPS, SPARC…

Goals in Defining RISC-V

- open

- real

- avoiding over-architeching

RISC-V 听着有点像汇编语言界的 C 语言,简单又原始

User-Level ISA

A mandatory base integer ISA

- I: Integer instruction

- Standard extensions

- M: Integer Multipliaction & Division

- F: FP

- D: DP

- ect

- Optional extensions

RISC-V assembly language

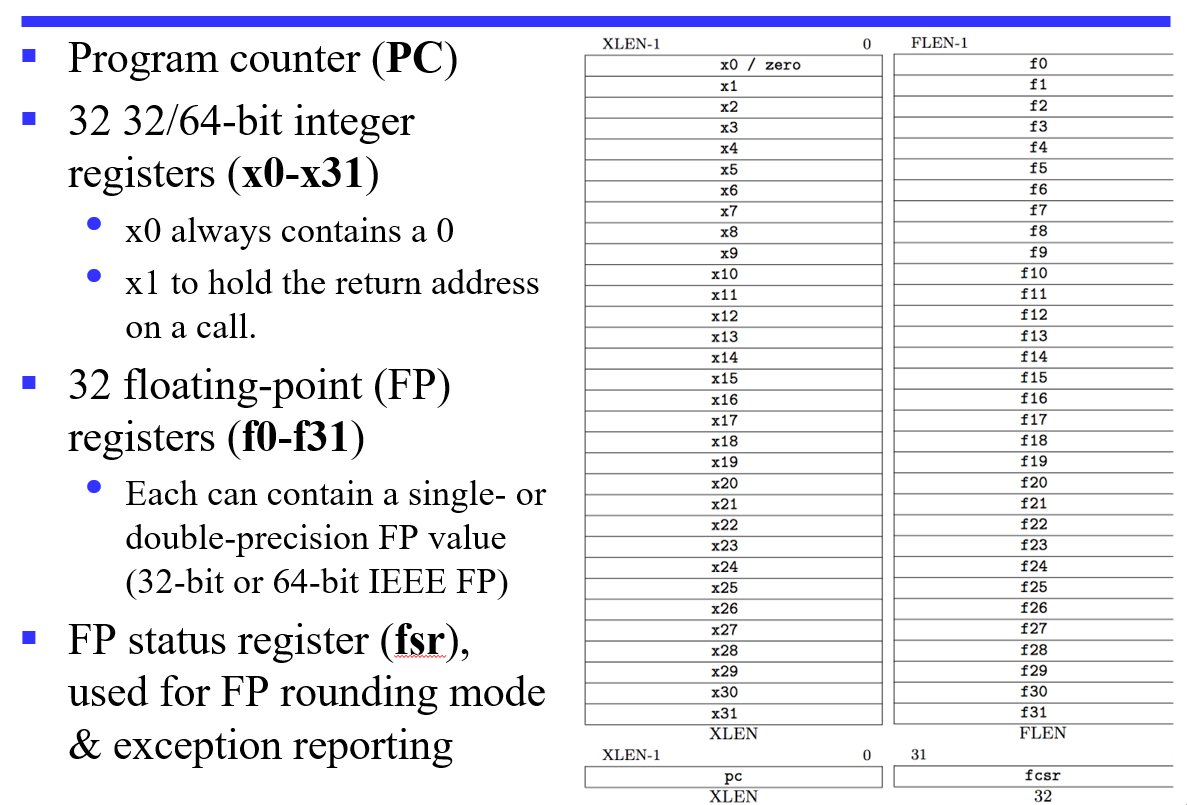

RISC-V Processor State

32 64-bit integer registers (x0 - x31)

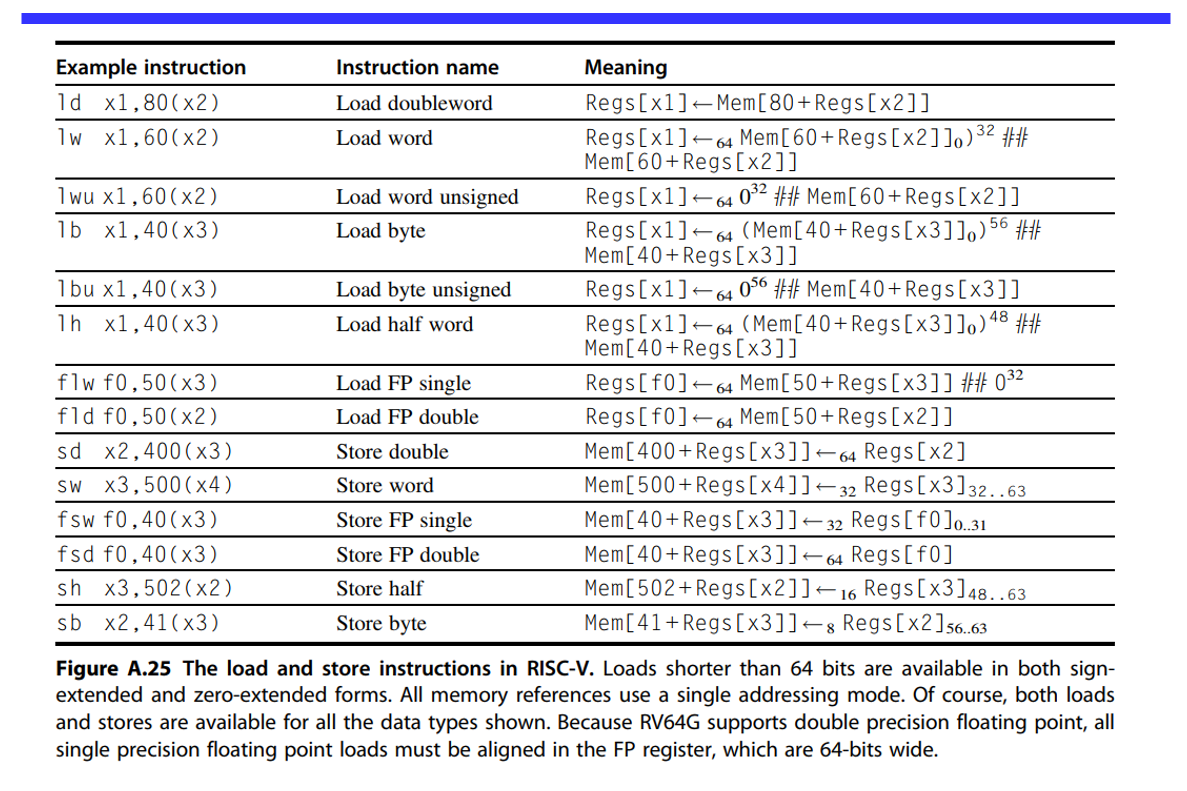

Load/Store Instruction

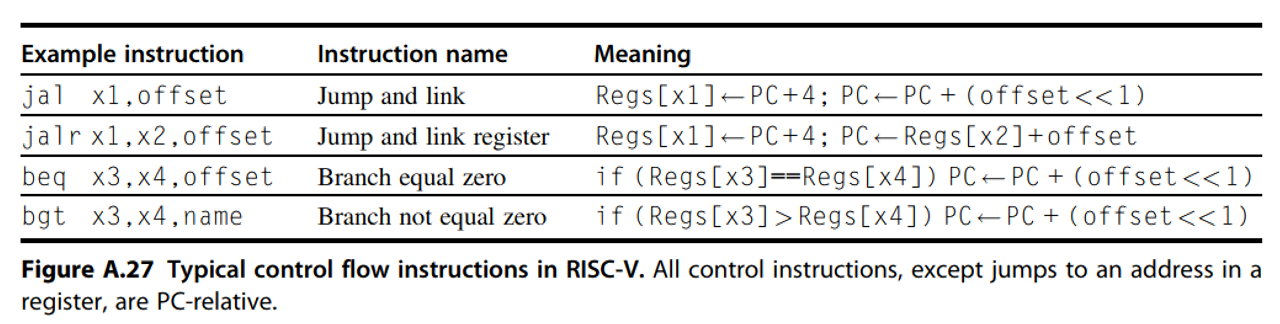

Control Transfer Instruction

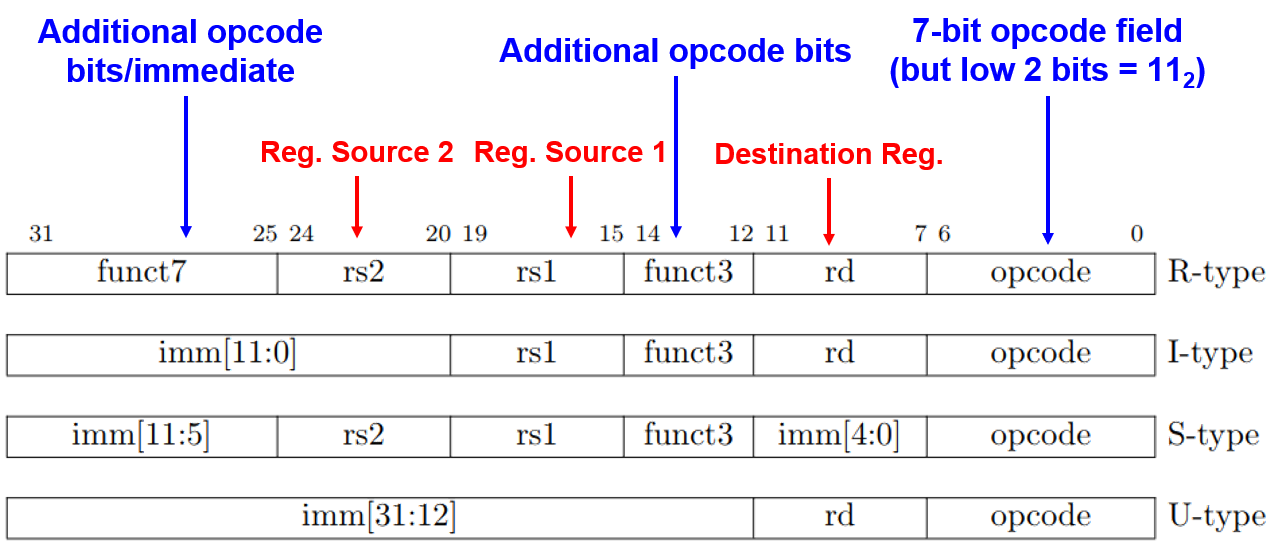

RISC-V Instruction Formats

https://github.com/riscv/riscv-opcodes/

RISC-V referrence card

- ALU Instruction: R-Type

- ALU Instruction: I-Type

- Load/Store Instruction: I/S-Type

- Control Transfer Instruction: J-Type